CPU的前世今生:从电子管到异构计算,芯片如何统治数字时代?

小邢哥 | 13年编程老炮,拆解技术脉络,记录程序员的进化史

Hello,我是小邢哥。

之前我们聊过的编程语言、数据格式、二进制,最终都要依赖一个核心硬件来执行——CPU(中央处理器)。

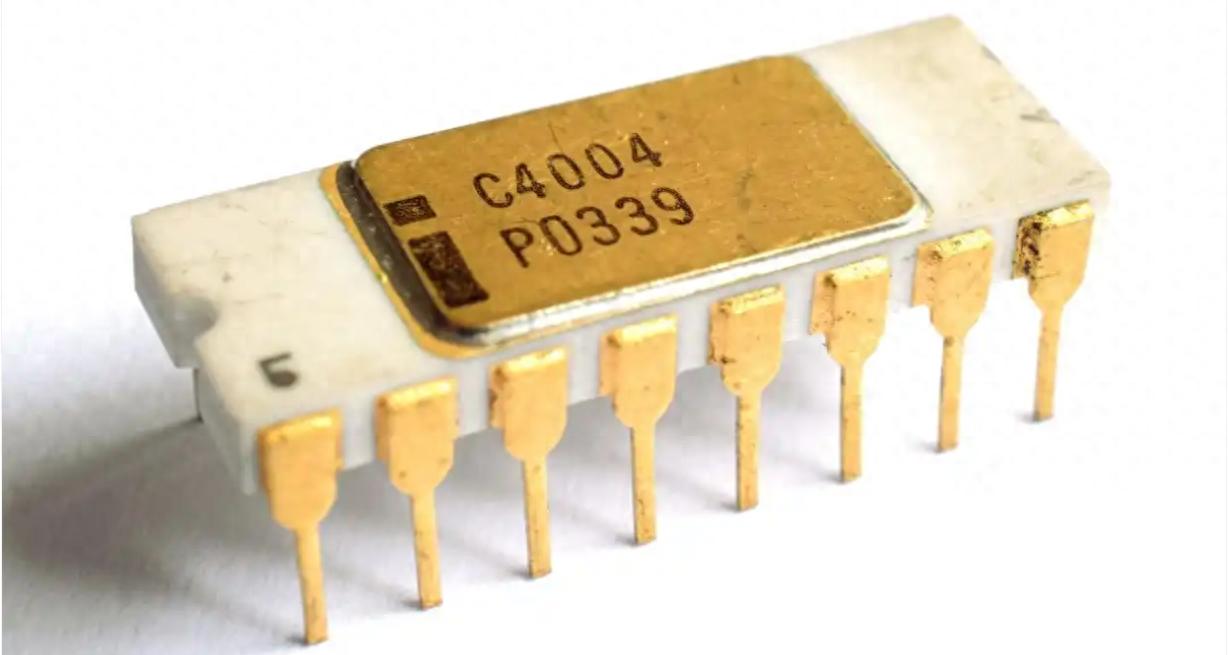

英特尔4004是世界上第一款微处理器

它就像数字世界的“大脑”,负责解读和执行每一条指令,从早期计算机的“房间大小”到如今指甲盖般的多核芯片,CPU的百年演进史,本质上是人类对“高效计算”的极致追求史,也是整个数字技术生态的底层支撑史。

今天就将带大家穿透芯片的金属外壳,梳理CPU从萌芽到巅峰的完整脉络:从机械计算的雏形到电子管的突破,从晶体管的革命到集成电路的爆发,再到如今多核、异构计算的未来方向。

我们不仅要回顾关键历史节点,更要拆解技术演进的底层逻辑——为什么CPU会长成今天的样子?每一次突破背后都解决了什么核心痛点?

一、萌芽期(1900s-1940s):从机械齿轮到电子管,计算的“史前时代”核心痛点:手工计算效率低下,无法应对复杂运算需求

19世纪末到20世纪初,科学研究、军事计算(如弹道轨迹)、商业统计等场景对计算的需求激增,但当时的计算完全依赖人工或机械计算器——比如法国数学家帕斯卡发明的加法器、英国巴贝奇设计的差分机,本质上都是“齿轮联动的机械装置”,运算速度慢、误差大,且只能处理简单的加减乘除。

二战期间,美国陆军为了快速计算炮弹弹道,召集了上百名女性计算员手工计算,一套弹道数据往往需要几天时间,严重影响作战效率。此时,“用电子设备替代手工计算”成为迫切需求,CPU的雏形就在这样的背景下诞生。

关键突破:电子管取代机械齿轮,开启电子计算时代

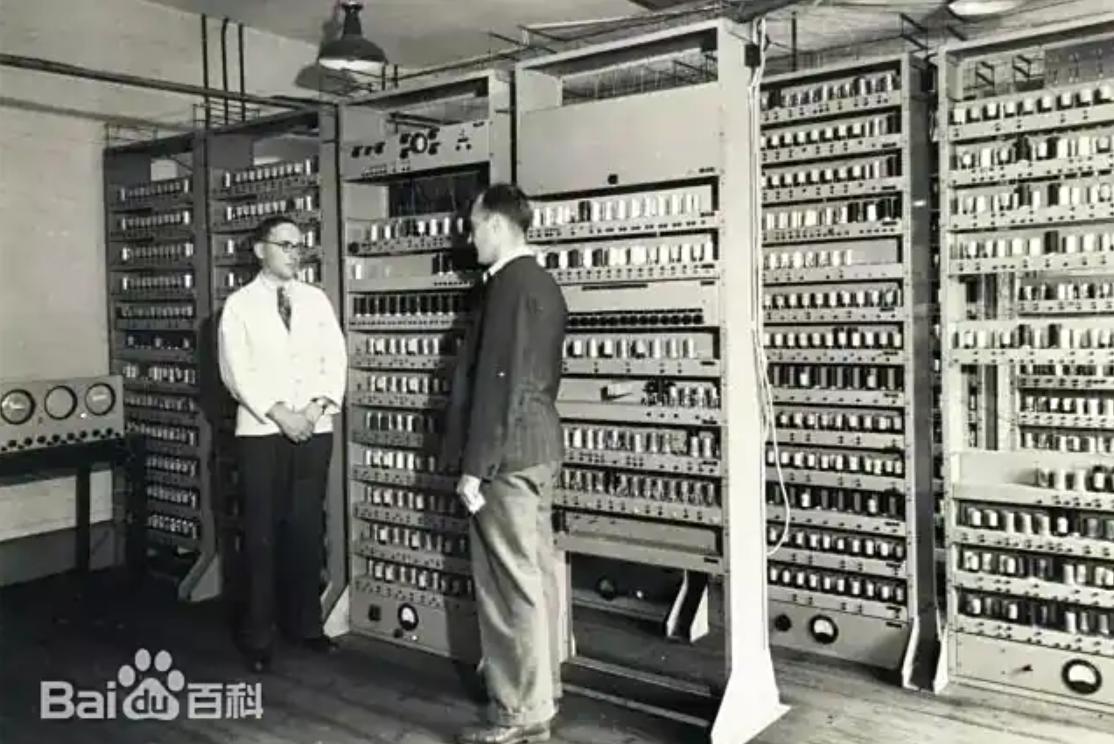

1946年,世界上第一台通用电子计算机ENIAC(电子数字积分计算机)在美国宾夕法尼亚大学诞生,它被视为CPU的“史前原型”。

1946年2月14日在美国宣告诞生

ENIAC的核心是18000个电子管,这些电子管替代了机械齿轮,通过“通电/断电”的二进制逻辑实现运算,运算速度达到每秒5000次加法,是手工计算的1000倍以上。

但ENIAC并非现代意义上的CPU——它没有统一的指令集和存储结构,运算需要通过插拔电缆、设置开关来配置,本质上是“专用计算设备”而非“通用处理器”。

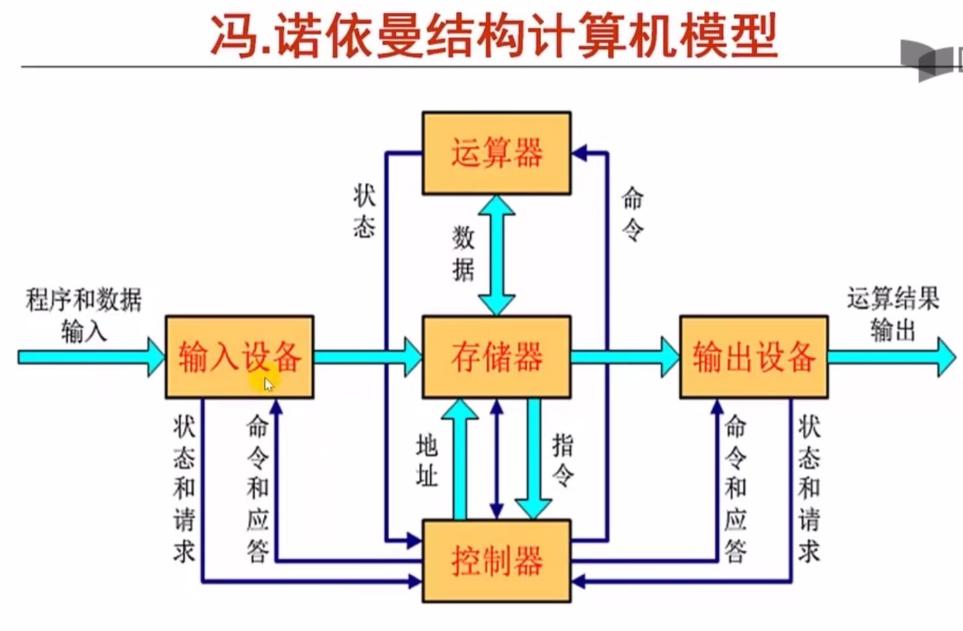

真正奠定CPU架构基础的,是冯·诺依曼在1945年提出的“冯·诺依曼体系结构”,其核心思想包括:

计算机由运算器、控制器、存储器、输入设备、输出设备五部分组成;指令和数据统一存储在存储器中,按顺序执行;采用二进制进行运算和存储。

这一架构直接定义了现代CPU的核心逻辑,直到今天,绝大多数CPU仍遵循这一设计思想。

历史细节:电子管的“先天缺陷”与早期探索

ENIAC的电子管存在致命问题:体积庞大(占地170平方米)、功耗极高(开机功率150千瓦,相当于1500个家用灯泡)、寿命短(平均几小时就有一个电子管烧毁)。

但它证明了“电子计算”的可行性,为后续CPU的发展指明了方向。

值得一提的是,英国在1943年就已研制出“科洛萨斯”计算机,同样采用电子管,主要用于破译二战期间德军“洛伦茨”加密机生成的高级密码,运算速度更快。

1943年主持建造的电子计算机,被认定为世界首台电子计算机

但因其军事机密属性,直到战后才被公开,且未采用冯·诺依曼体系(指令与数据未分离存储),仅为专用破解设备,故未成为通用计算的主流原型。

起步:从“手摇算盘”到“电子算盘”

早期机械计算器像“手摇算盘”,靠人力驱动齿轮运算;ENIAC的电子管则像“电动算盘”,靠电力驱动电子开关,速度大幅提升,但体积和功耗的问题,注定它只能是“实验室产物”,无法普及。

二、晶体管时代(1950s-1960s):CPU的“瘦身革命”,从房间大小到桌面设备核心痛点:电子管体积大、功耗高、可靠性差,无法实现设备小型化

ENIAC的缺陷让电子计算难以走出实验室——要满足更复杂的计算需求,就需要更多电子管,而更多电子管意味着更大的体积、更高的功耗和更低的可靠性。

1950年代,美国贝尔实验室的科学家们开始寻找电子管的替代方案。

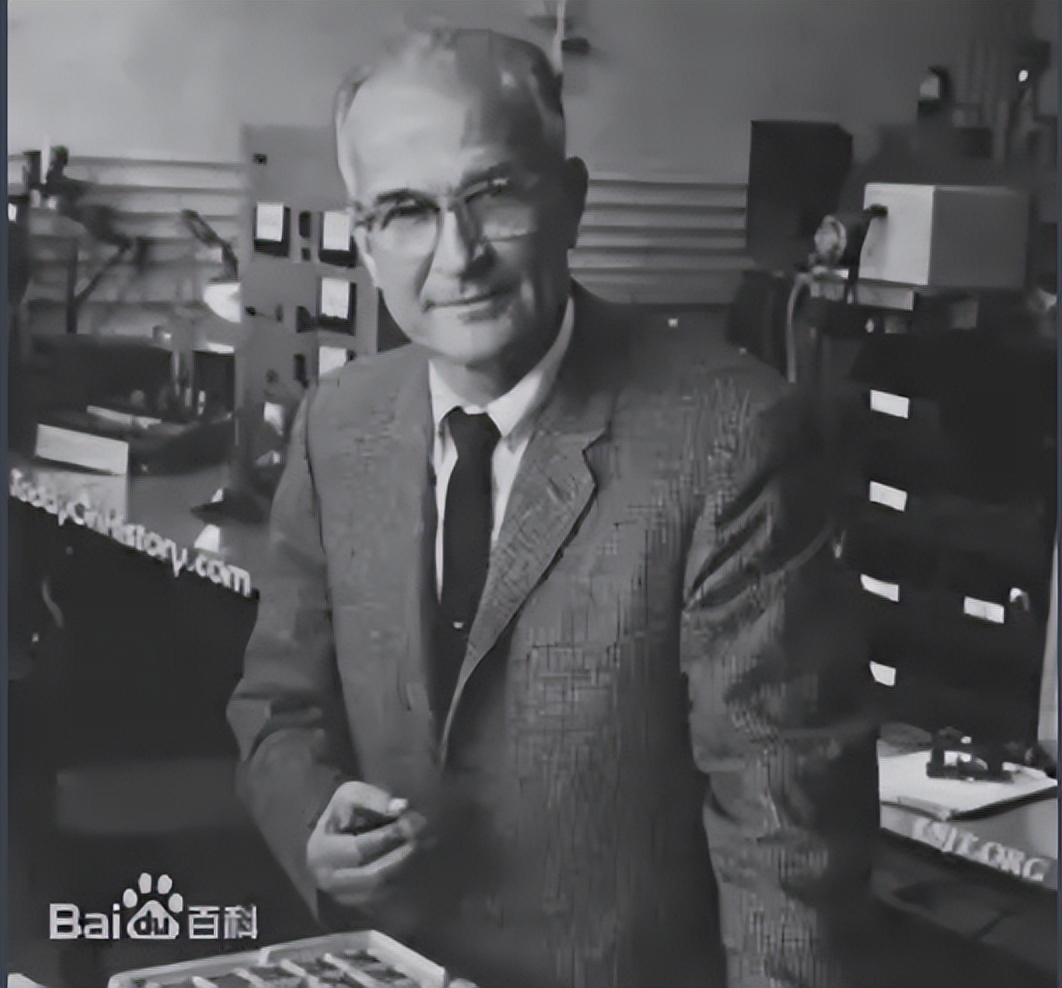

关键突破:晶体管的发明,奠定现代CPU的硬件基础

1947年,贝尔实验室的威廉·肖克利、约翰·巴丁、沃尔特·布拉顿三人发明了晶体管——一种仅指甲盖大小的半导体器件,能实现电子管的“开关”和“放大”功能,但体积只有电子管的1/1000,功耗只有1/100,寿命更是长达数万小时。

晶体管之父,威廉·肖克利,William Shockley

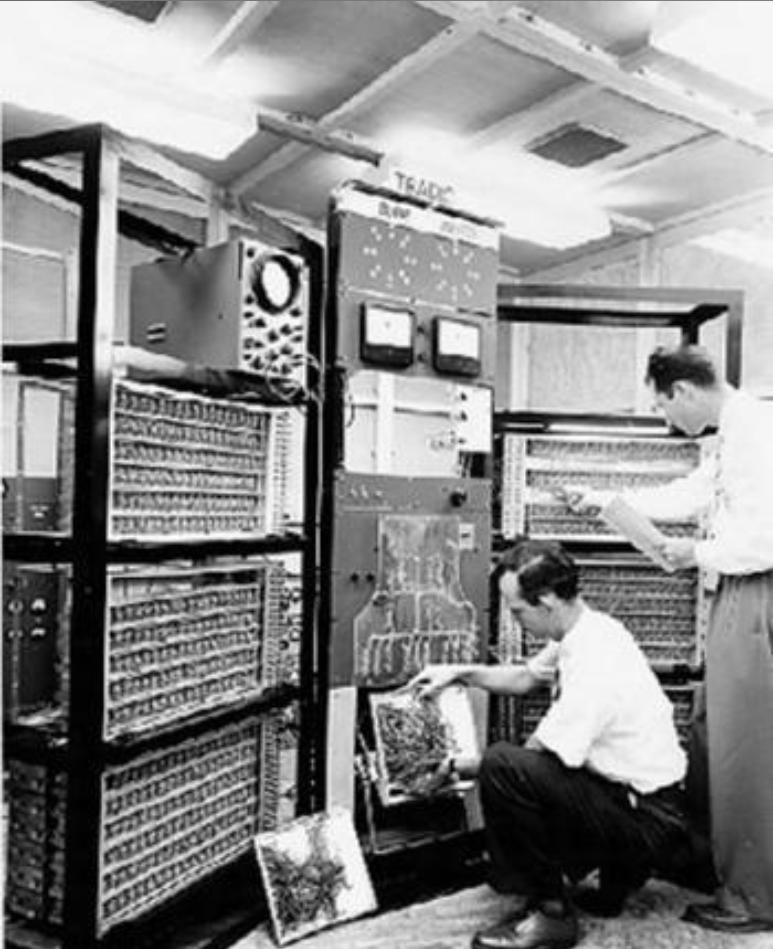

1954年,第一台晶体管计算机TRADIC诞生,仅用800个晶体管,体积缩小到ENIAC的1/100,功耗降至100瓦,运算速度达到每秒10万次加法。

第一台晶体管计算机TRADIC

1958年,IBM推出的IBM 7090晶体管计算机,成为首个商业化的晶体管计算设备,被广泛应用于科研和企业场景。

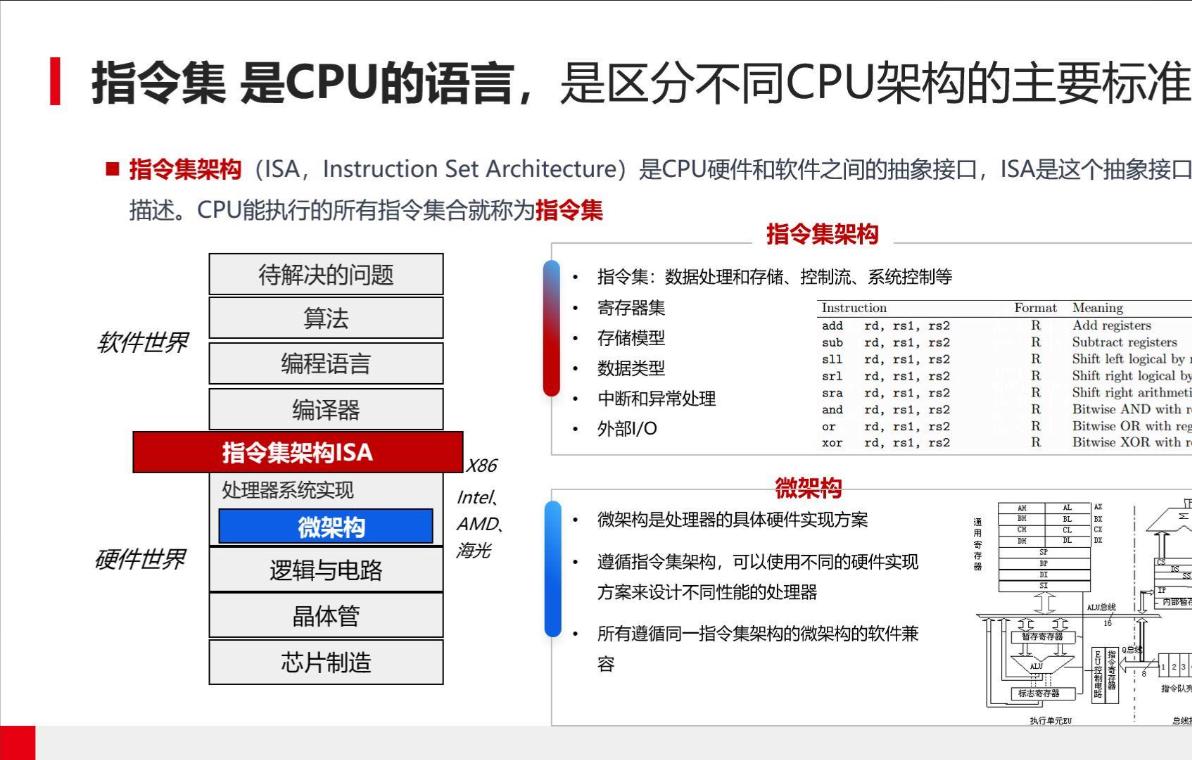

架构演进:指令集的诞生,CPU从“专用”走向“通用”

晶体管的普及让CPU的“通用化”成为可能。1950年代末,IBM率先提出“指令集”概念——将常见的运算(如加法、乘法、数据传输)封装成标准化的指令,CPU通过解读这些指令来执行任务。

这一设计让CPU摆脱了“专用设备”的局限,不同程序只需通过不同的指令组合,就能在同一台CPU上运行。

这一时期的指令集以“复杂指令集(CISC)”为主——指令数量多、功能复杂,旨在用一条指令完成复杂任务,减少指令执行次数。

CISC架构的代表是IBM的System/360系列计算机(1964年),其指令集成为后续x86架构的雏形。

历史意义:晶体管让CPU“走进大众视野”

晶体管的发明不仅解决了电子管的缺陷,更降低了计算设备的成本和门槛。

1960年代末,小型计算机(Minicomputer)开始兴起,CPU的体积缩小到桌面大小,价格降至企业和高校可承受范围,为后续个人计算机的爆发埋下伏笔。

IBM7090型全晶体管大型机

三、集成电路时代(1970s-1980s):CPU的“爆发期”,从企业专属到个人普及核心痛点:晶体管数量增长导致的布线复杂、成本上升

随着CPU性能需求提升,晶体管数量越来越多——1960年代末的小型计算机CPU已包含数千个晶体管,手工布线和组装的方式不仅效率低下,还容易出现故障,成本也随之飙升。

此时,“如何在更小的空间内集成更多晶体管”成为技术瓶颈。

关键突破:集成电路(IC)的发明,开启“摩尔定律”时代

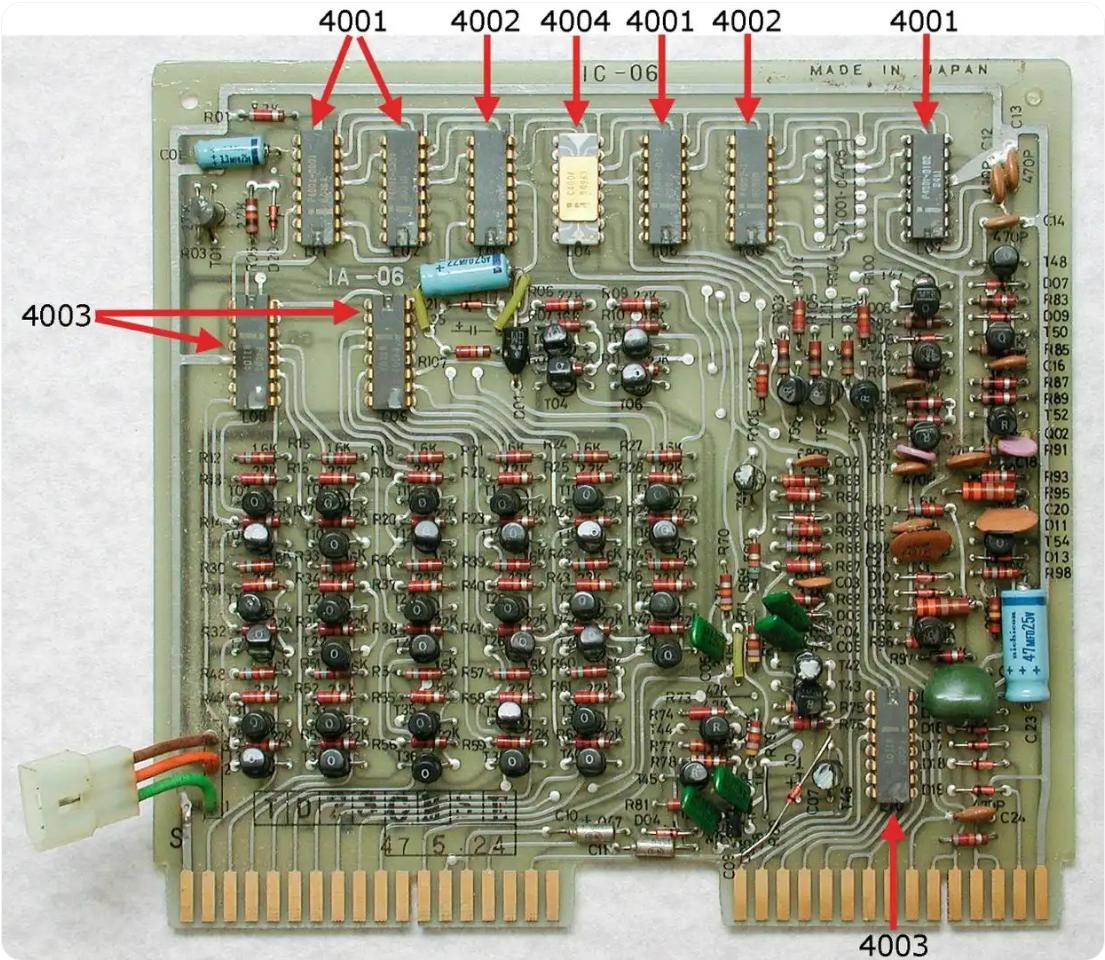

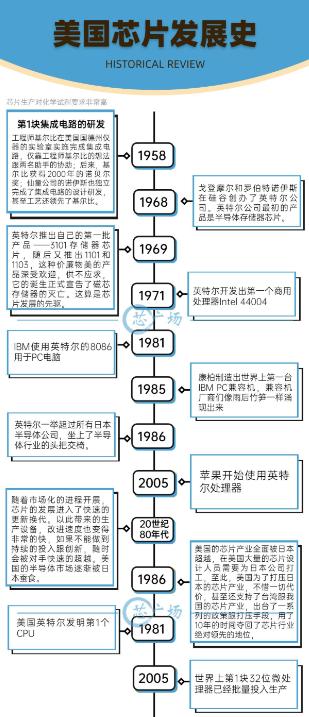

1958年,德州仪器的杰克·基尔比和仙童半导体的罗伯特·诺伊斯分别独立发明了集成电路(又称芯片) ——将多个晶体管、电阻、电容等元件集成在一块硅片上,通过光刻技术实现布线,彻底解决了晶体管组装的复杂问题。

1971年,英特尔推出了世界上第一颗通用微处理器——Intel 4004。这颗芯片仅4.2毫米×3.2毫米大小,集成了2300个晶体管,运算速度达到每秒6万次十进制加法(二进制运算速度更快),功耗仅1瓦,却能完成四则运算、数据传输等通用任务。

Intel 4004的诞生,标志着“CPU”正式成为独立的硬件组件,也开启了个人计算机的时代。

你敢想象这么小

摩尔定律的诞生与演进

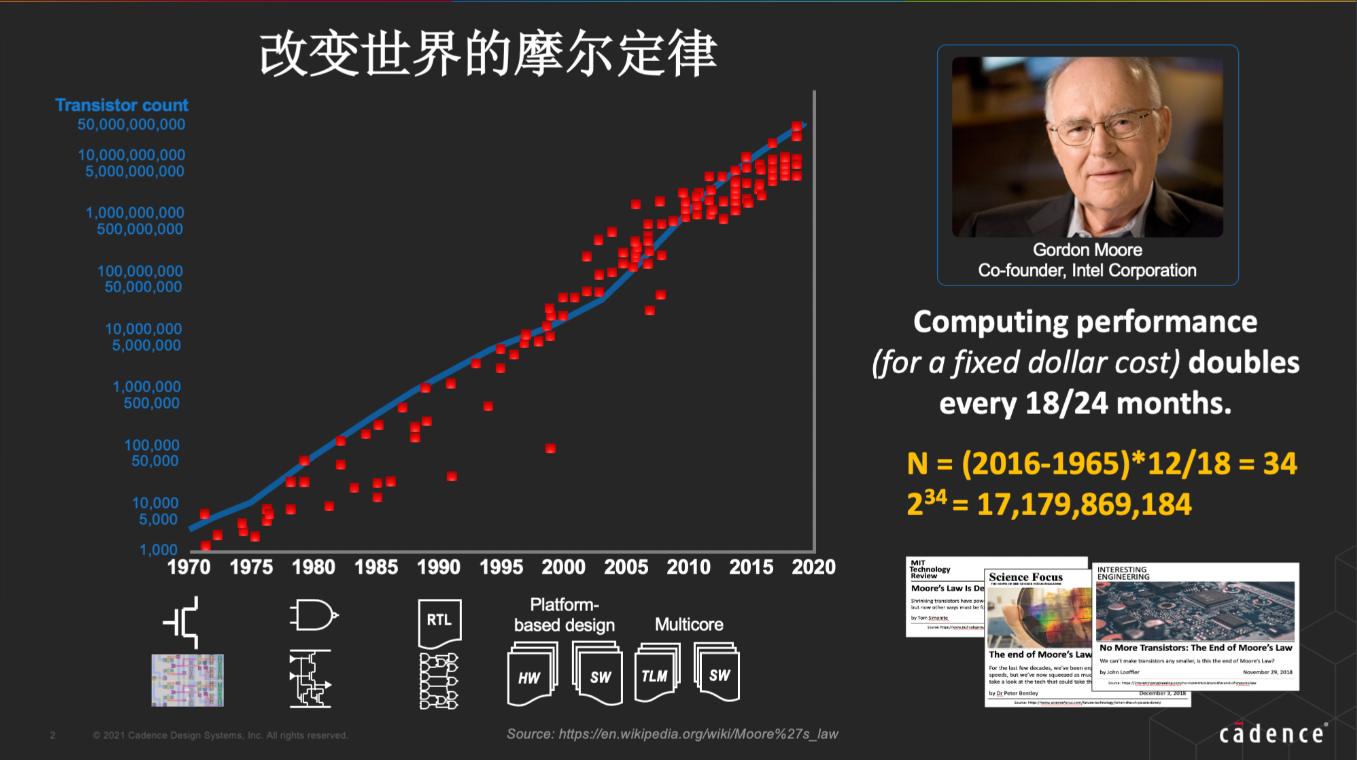

1965年,英特尔联合创始人戈登·摩尔在《电子学》杂志上发表文章,提出著名的“摩尔定律”:每18-24个月,集成电路上的晶体管数量将翻一番,性能也将提升一倍,而成本保持不变。

这一预测精准地指导了CPU的发展——从Intel 4004的2300个晶体管,到1982年Intel 80286的13万个晶体管,再到1985年Intel 80386的27.5万个晶体管,摩尔定律持续生效,成为CPU技术演进的“黄金法则”。

截至2025年,摩尔定律仍在延续,但“晶体管数量翻倍周期”已从最初的18-24个月延长至3-4年,且先进制程的研发成本呈指数级增长。

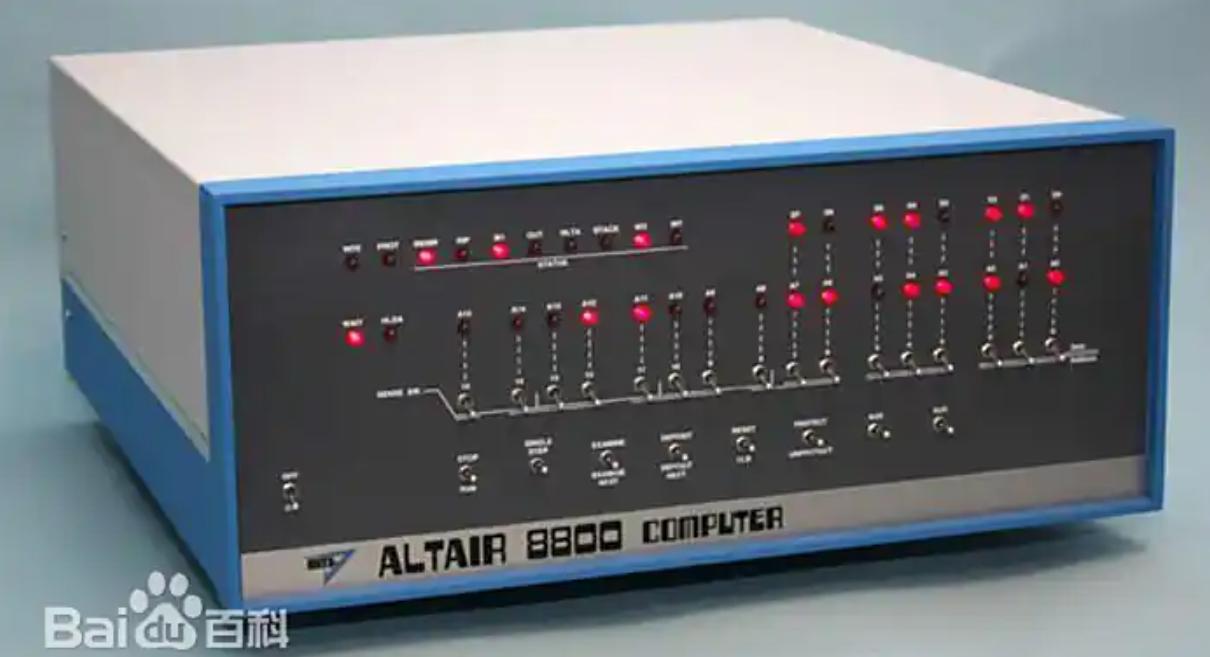

个人计算机爆发:CPU走进千家万户

1975年,第一台个人计算机Altair 8800诞生,搭载Intel 8080 CPU;1981年,IBM推出IBM 5150(首台IBM PC),搭载Intel 8088 CPU,标志着个人计算机正式商业化;1984年,苹果推出Macintosh,搭载摩托罗拉68000 CPU,通过图形界面让计算机更易操作。

这一时期的CPU架构呈现“双雄争霸”格局:Intel的x86架构(CISC)和摩托罗拉/苹果的68000架构(CISC变种),而后续RISC架构的崛起,为CPU的发展带来了新的方向。

这一时期:从“手工组装收音机”到“集成芯片收音机”

集成电路出现前,CPU的晶体管组装像“手工焊接收音机零件”,耗时耗力还容易坏;集成电路则像“收音机集成芯片”,所有零件都在一块硅片上,体积小、可靠性高、成本低,让CPU的大规模普及成为可能。

四、架构之争与多核时代(1990s-2010s):CPU的“效率革命”,从单核狂飙到多核协同核心痛点:单核CPU的性能瓶颈,频率提升遭遇功耗墙

1990年代到2000年代初,CPU性能提升主要依赖“提高时钟频率”——从Intel 80486的25MHz,到Pentium 4的3.8GHz,频率的提升直接带来运算速度的增长。

但到2005年左右,频率提升遭遇“功耗墙”:时钟频率超过4GHz后,CPU的功耗和发热呈指数级增长,散热成为无法解决的问题(比如Pentium 4的功耗达到130瓦,需要大型散热器才能稳定运行)。

同时,“架构之争”也进入白热化:CISC架构的指令集越来越复杂,导致CPU硬件设计繁琐、执行效率低下;而1980年代诞生的“精简指令集(RISC)”,通过简化指令数量、优化指令执行流程,在同等晶体管数量下实现了更高的能效比。

关键突破1:RISC架构的崛起与ARM的逆袭

RISC架构的核心思想是“精简指令、单周期执行”——去除CISC中不常用的复杂指令,让每个指令都能在一个时钟周期内完成,从而提升执行效率。

需要明确的是,RISC的理论基础由加州大学伯克利分校在1980年提出(RISC-I项目),ARM并非RISC的起源,而是将其商业化并推向嵌入式市场的核心厂商。

1985年,ARM(Advanced RISC Machines)成立,推出ARM 1处理器,凭借低功耗、高性能的优势,迅速占领嵌入式设备市场(如手机、路由器)。

1990年代末,移动互联网兴起,ARM架构的低功耗特性成为手机CPU的首选——2007年iPhone发布,搭载ARM架构的三星S5L8900 CPU;2010年iPad发布,搭载ARM架构的A4 CPU。

如今,全球90%以上的移动设备CPU都采用ARM架构,形成了“x86统治桌面/服务器,ARM统治移动设备”的格局。

关键突破2:多核架构的普及,突破单核功耗墙

面对单核频率的瓶颈,CPU厂商转向“多核协同”——在一颗芯片上集成多个独立的运算核心,通过并行计算提升性能,同时控制单个核心的频率和功耗。

2005年,AMD率先推出双核CPU Athlon 64 X2;2006年,英特尔推出Core 2 Duo双核CPU,标志着CPU正式进入多核时代。

多核架构的核心逻辑是“并行处理”——比如同时打开浏览器、办公软件、音乐播放器时,CPU会分配不同的核心处理不同的任务,避免单核心过载。随着技术发展,核心数量从双核、四核,逐步增长到如今服务器CPU的64核、128核,个人电脑CPU的8核、16核。

关键突破3:超线程与缓存优化,提升多核利用率

为了进一步提升多核效率,CPU厂商推出了两项关键技术:

超线程(Hyper-Threading):让单个核心能同时处理两个线程,相当于“虚拟双核”,提升核心利用率(比如英特尔的Core i7系列率先支持超线程);多级缓存(Cache):在CPU内部集成高速缓存(L1、L2、L3),减少CPU与内存之间的数据传输延迟——内存的读写速度仅为CPU运算速度的1/100,缓存的存在让CPU能快速获取常用数据,大幅提升性能。

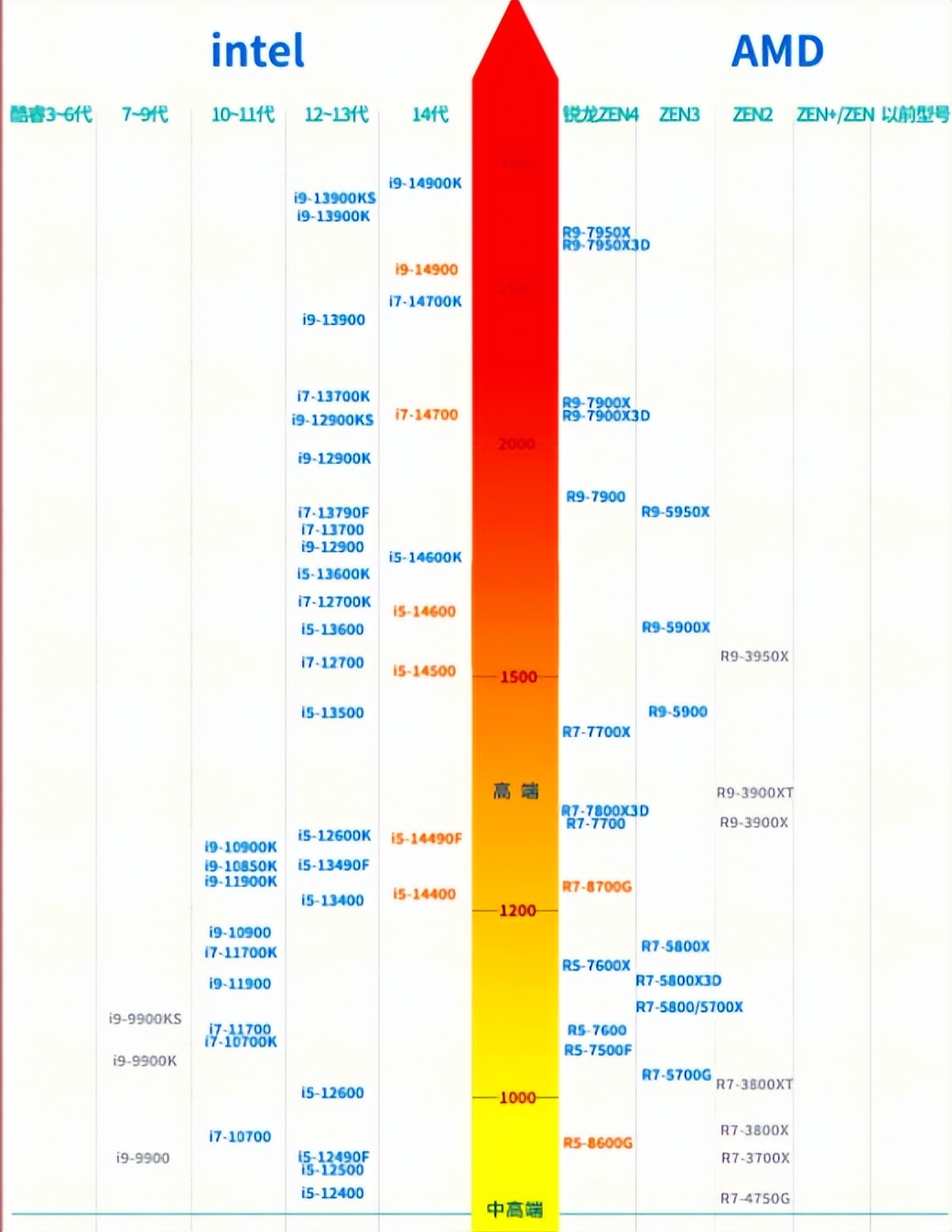

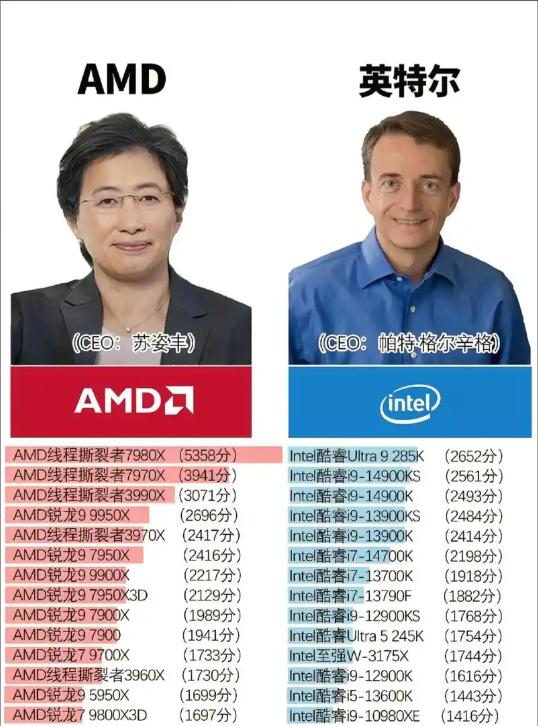

历史细节:Intel与AMD的“x86争霸战”

1990年代到2000年代,英特尔和AMD在x86架构市场展开激烈竞争:英特尔凭借Pentium系列占据主导地位,AMD则通过Athlon系列在性价比市场突围。

2003年,AMD推出64位x86-64架构,率先实现64位计算,迫使英特尔跟进;2006年,英特尔Core系列凭借更优的能效比反超AMD,重新占据市场主导地位。

这场竞争推动了x86架构的快速迭代,也让消费者受益于性能提升和价格下降。

五、现代与未来(2010s-至今):异构计算与专用加速,CPU的“全能进化”核心痛点:通用计算无法满足专用场景需求,能效比待提升

随着AI、大数据、云计算、游戏等场景的爆发,通用CPU的局限性逐渐显现:AI模型的矩阵运算、游戏的图形渲染、视频的编解码等任务,需要特定的运算逻辑,通用CPU的“面面俱到”导致能效比低下——比如用通用CPU训练AI模型,速度慢且功耗高,远不如专用芯片高效。

关键突破1:异构计算架构,通用核心+专用加速器

为了解决专用场景的效率问题,现代CPU开始采用“异构计算”架构——在一颗芯片上集成“通用计算核心(CPU)”和“专用加速核心”,各司其职:

典型代表包括:

关键突破2:先进制程工艺,延续摩尔定律

虽然摩尔定律的增速有所放缓,但先进制程工艺的进步仍在推动CPU性能提升。

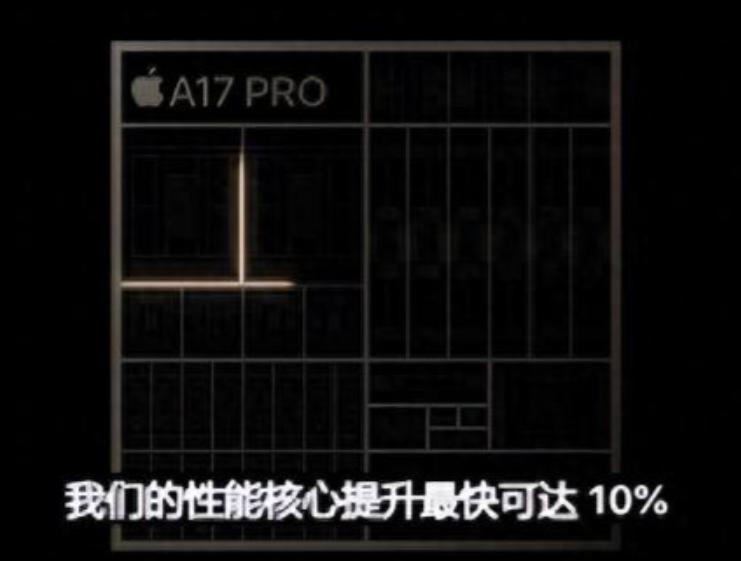

制程工艺从2010年的32nm,演进到2015年的14nm,再到2020年的7nm、5nm,2023年的3nm——制程越先进,单位面积内的晶体管数量越多,核心电压越低,功耗和发热也越小。

目前,台积电、三星是全球领先的先进制程代工厂商,英特尔也在加速推进先进制程(如Intel 4制程,相当于7nm)。

3nm制程的CPU(如苹果A17 Pro、高通骁龙8 Gen 3)已广泛应用。

关键突破3:软件与硬件协同优化,释放硬件潜力

现代CPU的性能提升,不再仅依赖硬件升级,还需要软件的协同优化:

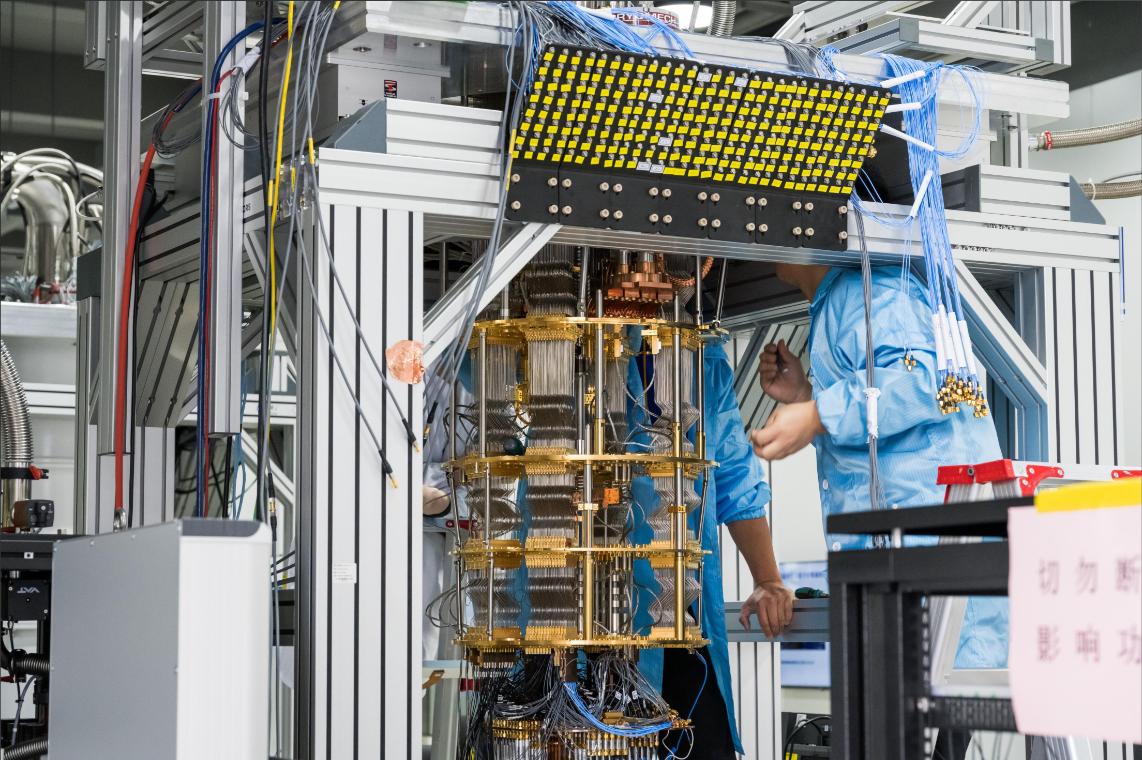

未来趋势:专用化、智能化、异构融合专用计算进一步强化:AI、量子计算、边缘计算等场景的专用加速器会越来越多,CPU将成为“异构计算的调度中心”,而非唯一的运算核心;

智能化管理:CPU将集成更多传感器,实时监控温度、功耗,动态调整核心频率和电压,实现“性能与功耗的智能平衡”;量子计算融合:量子CPU(QPU)与传统CPU的融合,可能在特定场景(如密码破解、材料模拟)实现突破性性能;能效比优先:随着碳中和需求提升,CPU的能效比(性能/功耗)将成为核心指标,而非单纯追求峰值性能。六、CPU演进的核心逻辑:从“单一性能”到“场景适配”

回顾CPU的百年发展史,其技术演进始终围绕两个核心问题:如何提升运算效率?如何适配不同场景需求?

背后的逻辑可以总结为三点:

1. 硬件基础的迭代:从“机械”到“电子”再到“集成”

2. 架构设计的优化:从“通用”到“专用”再到“异构”

3. 发展目标的转变:从“追求峰值性能”到“追求综合能效”

早期CPU的目标是“越快越好”,通过提升频率、增加晶体管数量实现;如今的目标是“在合适的功耗下,满足场景需求”——移动设备追求低功耗,服务器追求高并发,桌面设备追求性能与功耗平衡,这种“场景化能效比”成为CPU设计的核心导向。

总结:CPU的胜利,是“技术迭代与场景适配”的双重胜利

从ENIAC的电子管到如今的3nm异构芯片,CPU的百年演进史,是人类科技进步的缩影。

它的每一次突破,都不是孤立的技术创新,而是对时代需求的精准回应——二战的军事需求催生了电子计算,个人计算机的普及推动了微处理器的发展,移动互联网的爆发成就了ARM架构,AI的崛起引领了异构计算。

对我们开发者和技术爱好者来说,CPU的演进逻辑也带来了重要启示:技术的价值不在于“复杂先进”,而在于“解决实际问题”。

就像CPU从“追求单一性能”到“场景化适配”的转变,我们在选择技术、设计产品时,也应聚焦“需求本质”,而非盲目追求“技术炫技”。

如今,CPU已不再是单纯的“运算工具”,而是数字世界的“核心枢纽”——连接着软件与硬件,适配着通用与专用场景,支撑着从手机、电脑到服务器、物联网设备的所有数字产品。

而随着技术的不断演进,这颗“数字大脑”还将继续进化,推动人类向更高效、更智能的数字时代迈进。